Lines 5-20 define the pin locations of the input switches and lines 25-40 define the pin locations of the output LEDs. In the Sources pane, expand the Constraints folder and double-click lab1.xdc entry to open the file in text mode. Open the lab1_basys3.xdc or lab1_nexys4.xdc source and analyze the content. Lines 19-24 describe the functionality, while line 26 assigns computed values to the output signals led.

Line 15 declares an internal signal to build the LED state. Line 13 declares the architecture called Behavioral of the lab1 entity. Two std_logic vectors are used, 8 signals each: inputs swt (switches) and outputs led. Lines 8-11 declare the entity called lab1 and define the port interface signals. Lines 5-6 invoke the standard IEEE library and STD_LOGIC_1164 package. In the VHDL code, lines 1-3 are comment lines describing the entity name and the purpose of the module. In the Sources pane, double-click lab1.vhd entry to open the file in text mode. Open lab1.vhd source and analyze the content. Two directories, constrs_1 and sources_1, are created under lab1.srcs directory deep down under them, the copied lab1.xdc (constraint) and lab1.v (source) files respectively are placed. The lab1.cache directory is a placeholder for the Vivado program database. You will find that lab1.cache and lab1.srcs directories and the lab1.xpr (Vivado) project file have been created.

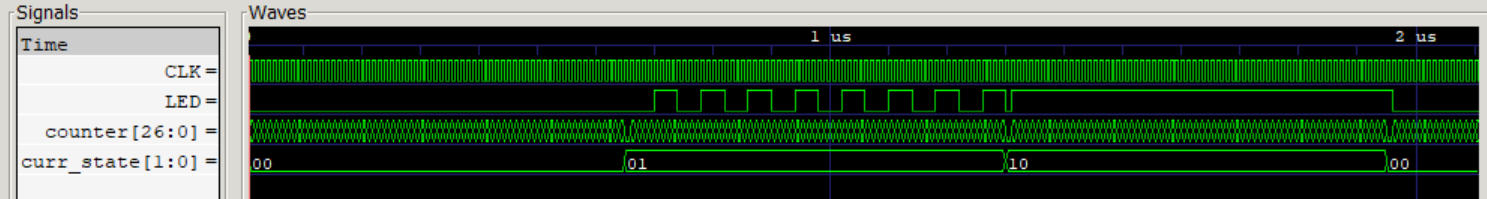

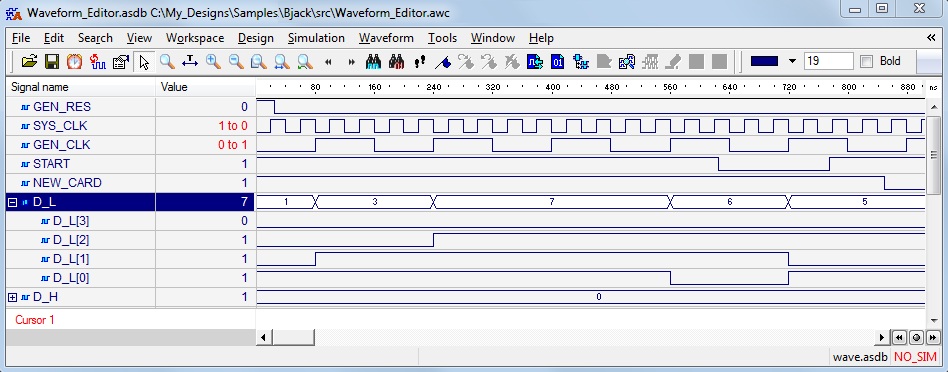

#Simple fpga simulation waveform windows#

Use the Windows Explorer and look at the C:\Digilent\Basys3Workshop\2020_1_artix7_labs\lab1 directory. Notice that Nexys4 and the Basys3 are not listed as they are not in the tool database.Ĭlick Finish to create the Vivado project. You can select the Boards Specify option, select Artix-7 under the Library filter, and select the appropriate board. In the Default Part form, using the Parts option and various drop-down fields of the Filter If using the Basys3 board, select the XC7A35TCPG236-1. This information can be obtained either through the board’s schematic or the board’s user guide. This Xilinx Design Constraints file assigns the physical IO locations on FPGA to the switches and LEDs located on the board. If no files are added, click on the Add Files… button, browse to the Downloads folder (if necessary), select lab1_basys3.xdc or lab1_nexys4.xdc and click OK (if necessary), and then click Next. Make sure that the Copy constrains files into project box is checked. Highlight and delete the XDC file not for the target board by clicking on the “X” on the right-hand side of the window. The constraint file lab1_basys3.xdc and lab1_nexys4.xdc are automatically added. Click Next to get to the Add Constraints form. Make sure that the Copy sources into project box is checked.

#Simple fpga simulation waveform simulator#

Selecting Target and Simulator languageĬlick on the Add Files button, browse to the Downloads folder, select lab1.vhd, click OK. Using the drop-down buttons, select VHDL as the Target Language and Mixed Simulator Language in the Add Sourcesįigure 3. Select RTL Project option in the Project Type Make sure that the Do not specify sources at this time box is unchecked. Click Next.Ĭlick the Browse button of the Project location field of the New Project form, browse to C:/Digilent/Basys3Workshop/2020_1_artix7_labs, and click Select.Įnter lab1 in the Project name Make sure that the Create Project Subdirectory box is checked. You will see Create A New Vivado Project dialog box. Open Vivado by selecting Start > All Programs > Xilinx Design Tools > Vivado 2020.1> Vivado 2020.1Ĭlick Create New Project to start the wizard. Use the provided lab1.vhd and lab1.xdc files from the 2020_1_artix7_sources\lab1 Launch Vivado and create a project targeting the XC7A35TCPG236-1 (Basys3) and using the VHDL HDL. Step 2: Simulate the Design using Vivado SimulatorĬreate a Vivado Project using IDE (Step 1) Step 1: Create a Vivado Project using IDE Other inputs are logically operated on before the results are output on the remaining LEDs as shown in Figure 1.įigure 1. The design consists of some inputs directly connected to the corresponding output LEDs. Follow these detailed instructions to progress through lab1. This lab is broken into steps that consist of general overview statements providing information on the detailed instructions that follow. Configure the FPGA using the generated bitstream and verify the functionality.Simulate the design using the Vivado simulator.

0 kommentar(er)

0 kommentar(er)